Parallel Input Serial Output Shift Register Vhdl Code

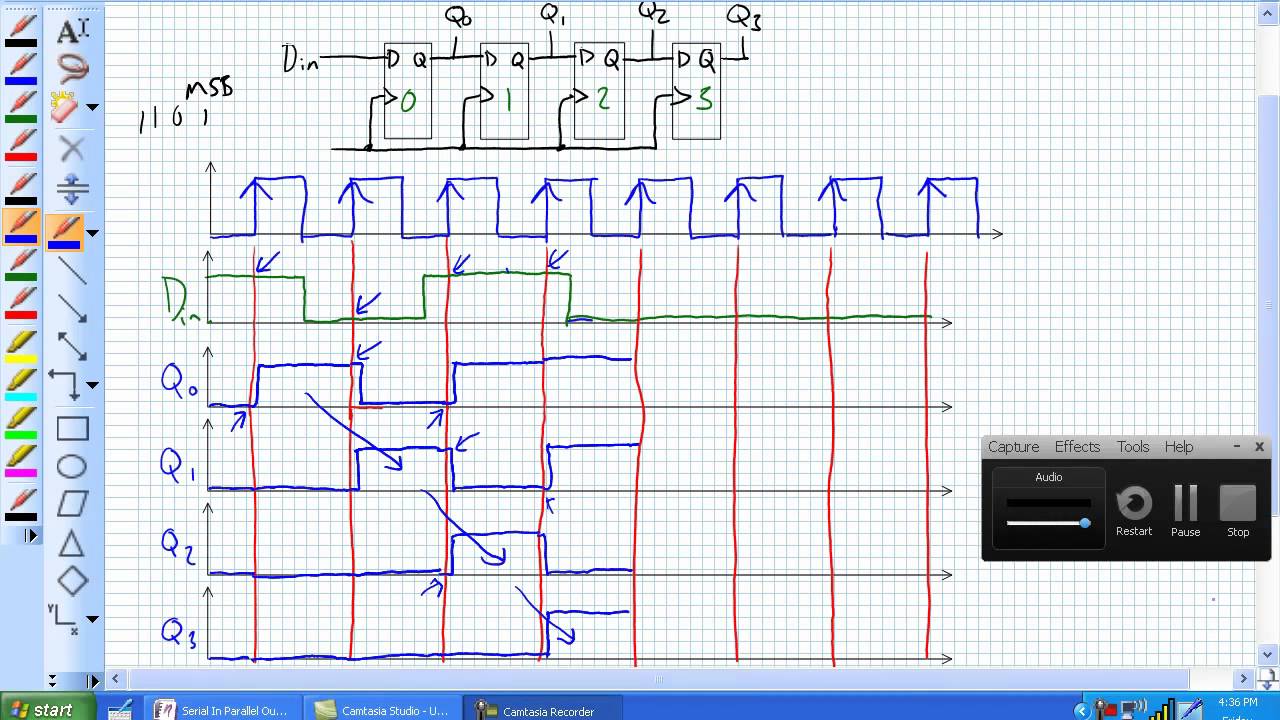

Two different ways to code a shift register in VHDL are shown. It is also possible to shift data from right to left and to use the LSB as an input for serial data. Shift Register VHDL Code. There are two examples of a shift register written in VHDL below. The two different examples create the same shift register using slightly different VHDL code. This video shows the VHDL shift register. Utilitech.

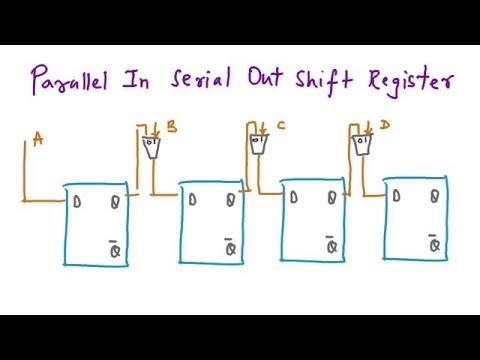

Parallel Input Serial Output Shift Registers

I am trying to take an 18 bit parallel load and change it into 9 two bit outputs using a shift register in vhdl. I have come up with the following code but am unsure of if I am thinking about this correctly.

Architecture rtl of x is signal two_shifter: std_logic_vector(1 downto 0); signal load_data: std_logic; signal shift_enable: std_logic; begin --Parallel to Serial shifter-- shifter: process(clk, reset) begin if (reset = '1') then two_shifter. I believe I understand what you were thinking, but your approach isn't correct.

Consider a single 9-bit version. You need a place to hold all 9 bits simultaneously when you load them in parallel, and then a 1-bit output for you to shift each bit out in series. Your design needs to double that, of course. A 2-bit register can only hold 2 bits at once - you have nowhere to store the rest of the 18 bits you want to load in parallel. Also, again, your input_reg process needs to be rethought - do you really want a serial-load function as well? – Mar 10 '14 at 15:46 •.